The external input and output timing ports are located on the CSM on the 7705 SAR-8 Shelf V2 and directly on the 7705 SAR-H and 7705 SAR-M. The 7705 SAR-A, 7705 SAR-Ax, and 7705 SAR-X have an external timing input port only, located on their faceplates. The external input timing port allows the SSU to be synchronized to an external timing reference. The external output timing port provides a synchronization output signal from the 7705 SAR to an external device. These external timing references typically would come from a GNSS, Building Integrated Timing System (BITS), or the external output timing ports from other telecom equipment.

The timing ports can be configured for the following:

2.048 MHz G.703 section 13 signal

5 MHz sine wave (not available on the 7705 SAR-8 Shelf V2 CSMv2)

10 MHz sine wave

On the 7705 SAR-18, the BITS ports 1 and 2 can be configured for the following:

2.048 MHz G.703 section 13 signal

T1 (ESF or SF)

E1 (PCM30CRC or PCM31CRC)

When redundant CSMs are used on the 7705 SAR-8 Shelf V2, the external synchronization inputs in each CSM must come from the same synchronization source; that is, you cannot select each input of the two CSMs as two of the three timing references. A Y-cable can be used to connect to a single reference connector. The synchronization output on each CSM is clocked by its own SSU clock.

On the 7705 SAR-18, either BITS port 1 or port 2 is available as an input and output source. When both inputs are connected and available, then the quality level (QL) from Synchronization Status Messaging (SSM) is used to determine which port is used by the CSMs as the BITS input. If SSM is not available, then BITS port 1 is the preferred input. BITS port 2 is used if BITS port 1 is not available. In this case, the operation is non-revertive. The BITS output ports 1 and 2 are clocked by the active CSM’s SSU clock.

The BITS output source command can be used to configure the BITS output ports’ source path on the 7705 SAR-18 to be either:

the filtered clock from the Synchronous Equipment Timing Generator (SETG)

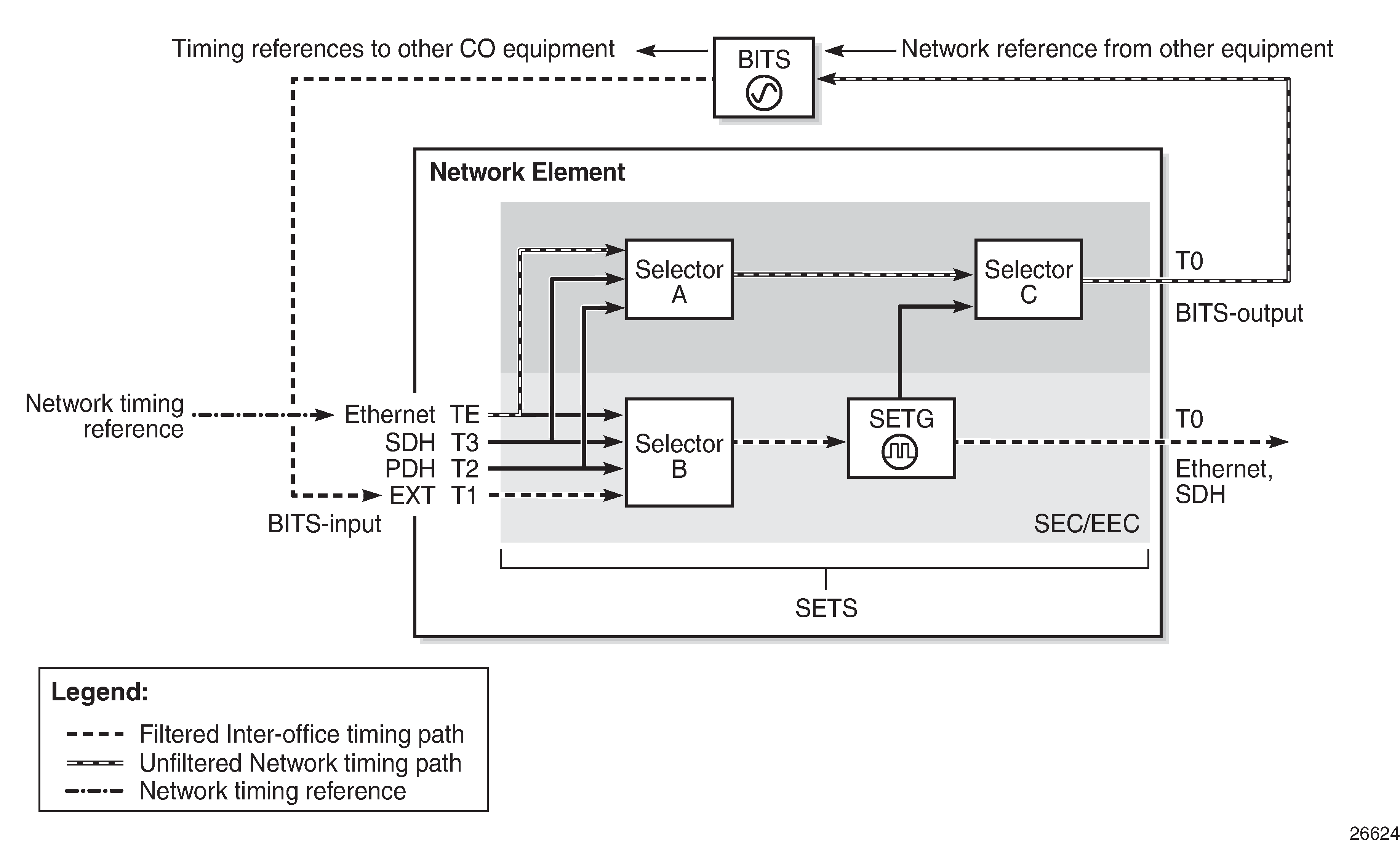

the alternate unfiltered path from the BITS output port via Selector A and C, as per ITU-T G.8262

Figure: BITS Timing Source Path shows an example of a timing source path. The BITS port is configured to deliver an input reference directly to a dedicated timing device such as a BITS or standalone synchronization equipment (SASE) device in a customer facility. The external BITS clock can have multiple references and can provide a common high-quality clock to all network elements at the customer location, including the 7705 SAR-18 node.

When configuring the priority order of the timing references with the ref-order command for unfiltered BITS output (T4), all reference sources are valid options, except the BITS input, which is excluded to avoid a timing loop. Because the same priority order is used for the SETG output (T0), the BITS input option must be set as the first (highest-priority) reference option.

Because both input and output clock pins are inside the physical RJ-45 port for each BITS port, a custom cable is required to connect input and output ports to different equipment. See the 7705 SAR-18 Chassis Installation Guide, BITS Ports and Pinouts.