PCR is a copper synchronous Ethernet-based, timing-over-packet technology. It is supported on the Packet Microwave Adapter card on the two copper RJ-45 synchronous Ethernet 1000Base-T Microwave Awareness (MWA) ports (ports 1 and 2) and on a copper SFP Ethernet port (ports 3 and 4).

There is no CLI configuration requirement for PCR; it is turned on automatically when a microwave link is enabled on an MWA RJ-45 port or on a copper SFP Ethernet port (ports 3 and 4).

On the MPR-e side, PCR requires that the MAC address of the 7705 SAR-8 Shelf V2 or 7705 SAR-18 be configured on the MPR-e radio that is connected to the 7705 SAR-8 Shelf V2 or 7705 SAR-18 chassis. See the latest version of the MPR-e user manual for the required information.

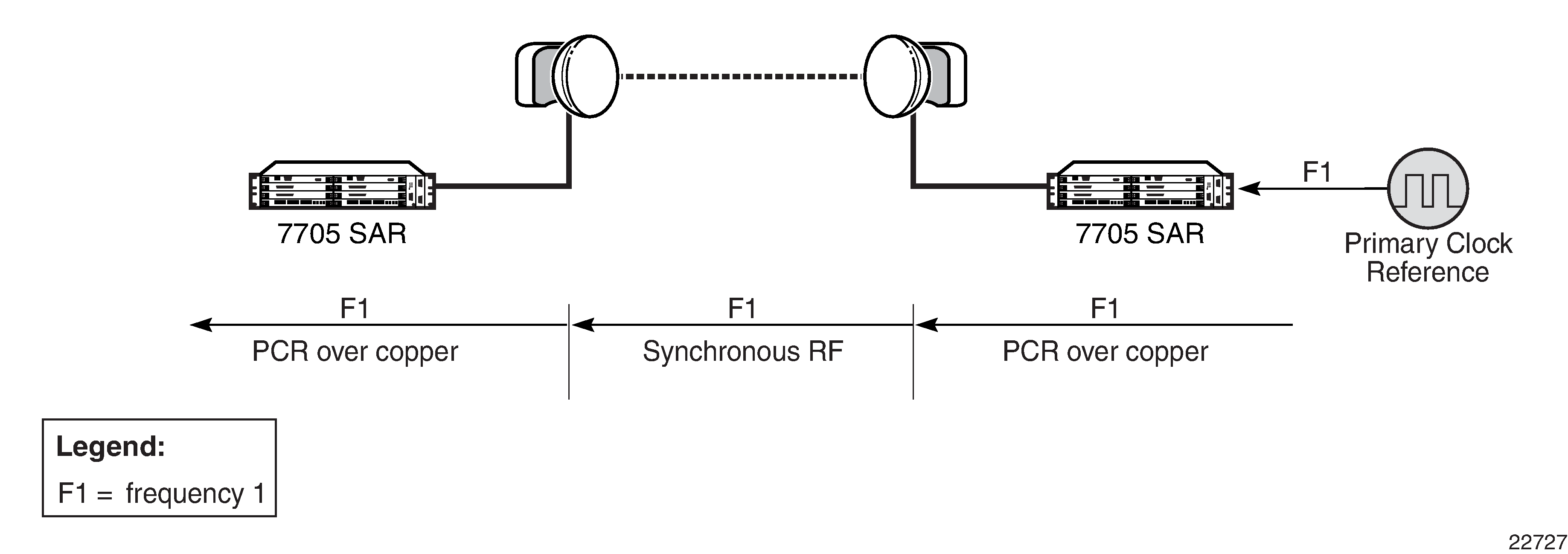

PCR provides the same frequency recovery capability as standard-based copper synchronous Ethernet without having to endure a traffic hit whenever a synchronous source switching occurs. See Figure: Proprietary Clock Recovery.

By running PCR between the MPR-e radio and the MWA port, frequency synchronization can be delivered in either direction. With standard-based copper synchronous Ethernet, there is a traffic hit every time a clock source change occurs on a 7705 SAR-8 Shelf V2 or 7705 SAR-18 because the 7705 SAR-8 Shelf V2 or 7705 SAR-18 and the MPR-e radio to which it is connected must bring down the Ethernet link MAC layer before it can renegotiate and reverse the master and slave clock role. This MAC layer renegotiation affects the data plane and the signaling and routing plane. All MPLS signaling links and the label switched path (LSP) are taken down during the renegotiation process; the routing signaling advertises the down state of the link throughout the network.

However, with PCR running on the microwave link, the physical layer transmit clock on a copper synchronous Ethernet port on the Packet Microwave Adapter card is always set to master. The reversal of the clock role only occurs at the PCR ‟layer”. This means that a synchronous source change does not disrupt the data plane and the signaling and routing plane on the 7705 SAR-8 Shelf V2 or 7705 SAR-18.